# 1.4 GBd Transmitter/Receiver Chip Set with **CIMT Encoder/Decoder and Variable Data Rate.**

# Description

The HDMP-1032A transmitter and HDMP-1034A receiver are used together to build a high-speed data link for point-to-point communication. These silicon bipolar transmitter and receiver chips are housed in standard plastic 64 pin PQFP packages.

From the user's viewpoint, these products can be thought of as a "virtual ribbon cable" interface for the transmission of data and control words. A parallel word loaded into the Tx (transmitter) chip is delivered to the Rx (receiver) chip over a serial channel and is then reconstructed into its original parallel form. The channel can be either a coaxial copper cable or optical link

The chip set hides from the user the complexity of encoding, multiplexing, clock extraction, demultiplexing and decoding. The CIMT encoding scheme used ensures the DC balance of the serial line. When data or control words

are not being sent the transmitter sends idle words.

The serial data rate of the Tx/Rx link is selectable in three ranges and extends from 208 to 1120 Mbit/s. This translates into an encoded serial rate of 260 to 1400 MBaud. The parallel data interface is 16 bit TTL. A flag bit is also present and can be used as an extra 17th bit under the user's control. This bit can be used as an even or odd word indicator for dual-word transmission. The encoding of the flag bit can be scrambled to reduce the probability of erroneous word alignment.

A user control space is also provided. If TXCNTL is asserted on the Tx chip, the least significant 14 bits of the data will be sent and the RXCNTL line on the Rx chip will indicate the data is a Control Word.

At the Rx, the PASS feature allows the recovered words to be clocked out with the local

Features

- 3.3 V supply, low power dissipation 660 mW Tx, 792 mW Rx

- On-chip encode/decode using **Conditional Inversion Master Transition (CIMT) protocol**

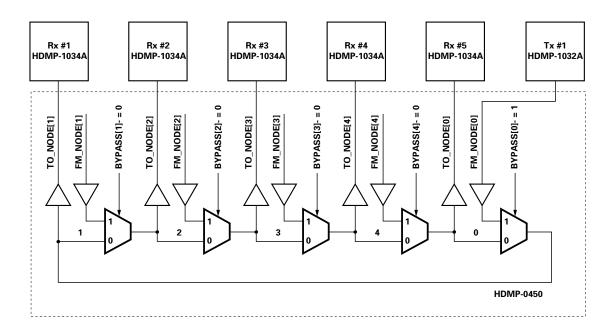

- 1:N broadcast ready configurable receiver inputs allow multi-point data broadcast using a single transmitter

- Parallel Automatic Synchronization System (PASS) allows receiver to read recovered words with local reference clock

- Robust simplex mode

- Wide range serial rate 260-1400 MBaud (user selectable)

- 5 V tolerant TTL interface 16 or 17 Bits wide

- Low cost 64 pin plastic package 14x14 mm<sup>2</sup> POFP

# Applications

- Cellular base station

- ATM switch

- Backplane/bus extender

- Video, image acquisition

- Point to point data link

- Implement SCI-FI standard

REFCLK. This feature is particularly useful when the Tx clock and REFCLK are synchronous. The PASS system also supports synchronization of multiple channels.

The chipset is compatible with previous versions of the G-Link chipset (HDMP-10x2/10x4) provided the latter are used in 16 bit Simplex with Periodic Sync Pulse or External Reference Oscillator Mode (Simplex Method II or III).

# **Table of Contents**

| Table of Contents                                    |     |

|------------------------------------------------------|-----|

| Topic P                                              | age |

| Typical Applications                                 | 3   |

| Setting the Operating Data Rate Range                | 4   |

| Transmitter Block Diagram                            | 5   |

| Receiver Block Diagram                               | 6   |

| Parallel Automatic Synchronization System            | 7   |

| Transmitter Timing                                   | 10  |

| Receiver Timing                                      | 11  |

| DC Electrical Specifications                         | 12  |

| AC Electrical Specifications                         | 12  |

| TXCLK and REFCLK Requirements                        | 13  |

| Absolute Maximum Ratings                             | 13  |

| Thermal Characteristics                              | 14  |

| I/O Type Definitions                                 | 14  |

| Pin-Out Diagrams                                     | 15  |

| Transmitter Pin Definitions                          | 16  |

| Receiver Pin Definitions                             | 18  |

| Mechanical Dimensions                                | 21  |

| Appendix: Internal Architecture Information          |     |

| Line Code Description                                |     |

| Data, Control, and Idle Word Codes                   | 22  |

| Tx Operation Principles – Encoding & Phase Lock Loop | 24  |

| Rx Operation Principles – Decoding & Phase Lock Loop | 25  |

| Integrator Capacitor & Power Supply                  |     |

| Bypassing/Grounding                                  | 26  |

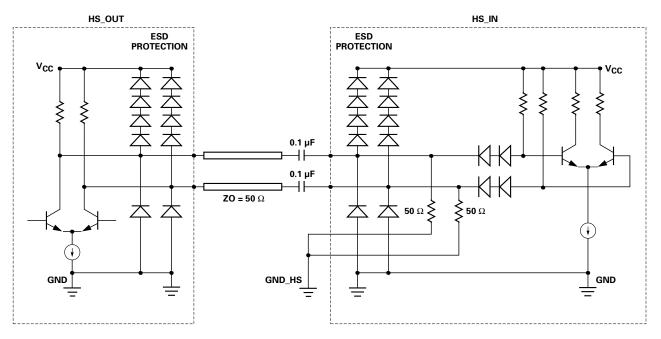

| TTL and High Speed I/O                               | 26  |

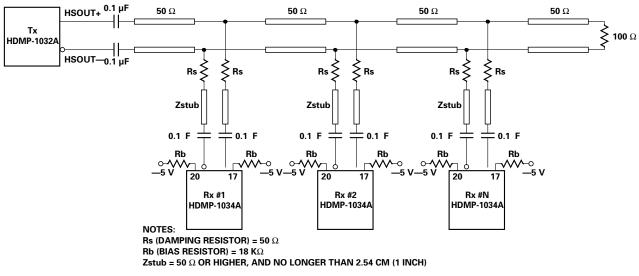

| Data Bus Line/Broadcast Transmission                 | 27  |

| Nomenclature Changes between                         |     |

| HDMP-1032A/34A and HDMP-1022/24                      | 30  |

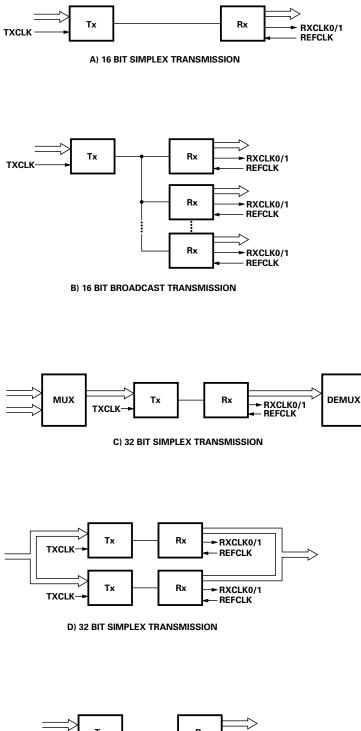

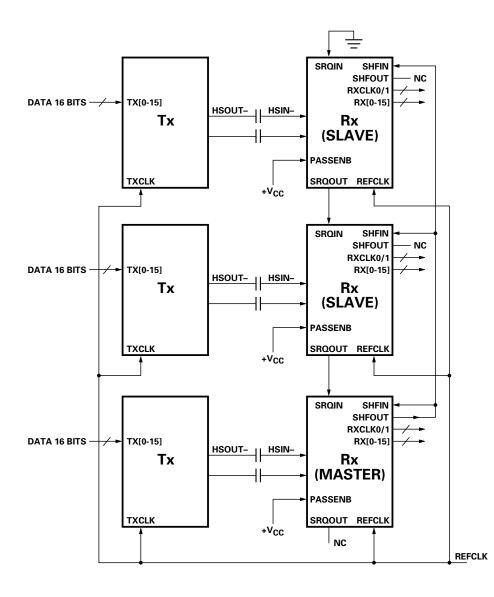

E) 16 BIT DUPLEX TRANSMISSION

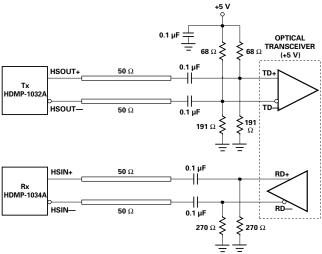

#### Figure 1. Various configurations using the HDMP-1032A/1034A.

#### **Typical Applications**

The HDMP-1032A/1034A chipset was designed for ease of use and flexibility. The customer can tailor the use of this product through the configuration of the link based on specific system requirements and application needs. Typical applications range from backplane serialization and bus extension to cellular base stations.

All modes are built up from the basic simplex transmission mode as shown in Figure 1a.

For digital video transmission, simplex links are common. The HDMP-1032A/1034A chipset can transmit 16 bits of parallel data in standard or broadcast simplex mode (Figures 1a, 1b).

If the bus is 32 bits wide, the HDMP-1032A/1034A chipset is capable of sending this data word as two separate word segments with the use of an external mux and demux as shown in Figure 1c. In this mode, the transmitter and receiver use the FLAG bit to indicate the first or second word segment. The HDMP-1032A/ 1034A chipset may also be configured in full duplex to achieve a 32 bit wide bus extension. In addition, 32 bit wide data can be transmitted over two parallel serial lines as shown in Figure 1d.

Low latency bus extension of a 16 bit wide data bus may be achieved using the full duplex configuration (Figure 1e). In this mode, link startup is achieved by exchange of control words.

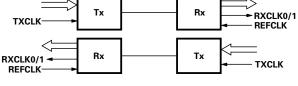

#### **Setting the Operating Data Rate Range**

The HDMP-1032A/1034A chipset can operate from 260 MBaud to 1400 MBaud. It is divided into three operating data ranges with each range selected by setting DIV1/0 as shown in the Typical Operating Rates table. Two examples have been provided in order to help in understanding and using this table.

#### Example 1 (Unique Range)

It is desired to transmit a 16 bit parallel word operating at a frequency of 60 MHz (60 MWord/ sec). Both the Tx and Rx must be set to a range that covers this word rate. According to the table only a setting of DIV1/0 = (0/0) allows a parallel input word rate of 40 to 70 MHz. This range setting easily accommodates the required 60 MHz word rate and is unique. The user serial data rate is calculated as:

Serial Data Rate =  $(\frac{16bits}{Word}) (\frac{60MW}{sec}) =$ 960 MBits/sec

The baud rate includes an additional four encoding bits (20 bits total) that the HDMP-1032A/34A G-Link chipset transmits. The serial baud rate is calculated as:

Serial Baud Rate =  $\left(\frac{20\text{bits}}{\text{Word}}\right) \left(\frac{60\text{MW}}{\text{sec}}\right) =$ 1200 MBaud

# Example 2 (Overlapping Ranges)

Some applications may have a parallel word rate that seems to fit in two ranges of operation. For example, a 42.5 MHz (42.5 MWord/s) parallel data rate falls within two ranges: DIV1/0 = (0/0) and DIV1/0 = (0/1). According to the table, a

setting of DIV1/0 = (0/1) gives an upper rate of 45 MHz while a setting of DIV1/0 = (0/0) gives a lower rate of 40 MHz. The upper and lower data rates stated in the tables are <u>typical</u> values unless indicated by (min) or (max) and may vary between individual parts. However, each transmitter/receiver has overlapping ranges of operation providing continuous band coverage from 260 to 1400 MBaud.

In this example, each transmitter/ receiver will permit a 42.5 MHz parallel data rate but it is suggested that DIV0 be tied to a jumper that can be set either to logic '1' (open allowing DIV0 to float high) or logic '0' (ground). This allows the design to accommodate both ranges for maximum flexibility. This technique is recommended whenever operating near the upper and lower ends of two adjacent word rate ranges.

# HDMP-1032A (Tx), HDMP-1034A (Rx) Typical Operating Rates<sup>1,2</sup>

$T_{c} = -20^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 3.15V$  to 3.45V

|      |      |          | Parallel Word Rate<br>(MWord/sec) |           | a Rate<br>c) | Serial Ba<br>(MBaud) | ud Rate    |

|------|------|----------|-----------------------------------|-----------|--------------|----------------------|------------|

| DIV1 | DIVO | Rang     | e                                 | Range     | 9            | Range                | )          |

| 0    | 0    | 40       | 70 (max)                          | 640       | 1120 (max)   | 800                  | 1400 (max) |

| 0    | 1    | 20       | 45                                | 320       | 720          | 400                  | 900        |

| 1    | 0    | 13 (min) | 26                                | 208 (min) | 416          | 260 (min)            | 520        |

Figure 2. Typical data rates showing ranges of operation<sup>1</sup>.

#### Notes:

All values in this table and graph are typical unless otherwise noted by (min) or (max), (min) indicates a minimum guaranteed value, (max) indicates a maximum guaranteed value.

2. All values in this table are expected for a BER less than 10<sup>-14</sup>.

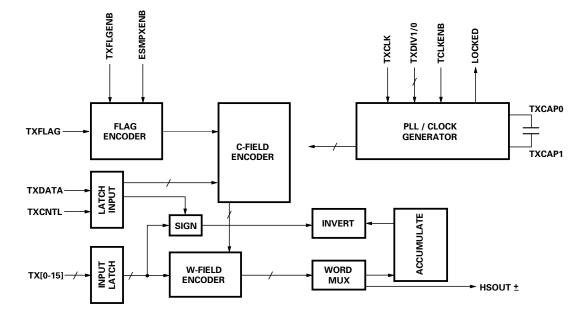

#### HDMP-1032A Tx Block Diagram

The HDMP-1032A transmitter was designed to accept 16 bit wide parallel words and transmit them over a high-speed serial line. The HDMP-1032A performs the following functions:

- Latching parallel word input

- Phase lock to TXCLK

- High speed clock multiplication

- Word encoding

- Parallel to Serial Multiplexing

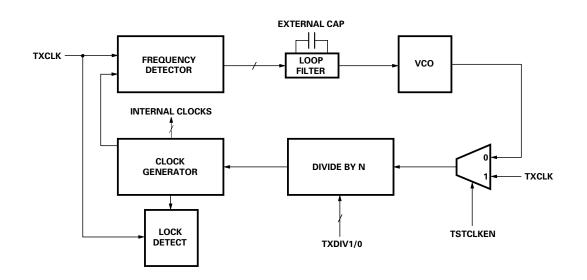

# **PLL/Clock Generator**

The Phase Lock Loop and Clock Generator are responsible for generating all the internal clocks needed by the transmitter to perform its functions. These clocks are based on a supplied word clock (TXCLK) and control signals (TXDIV1/0, TCLKENB). TXCLK is the incoming word clock. The PLL/Clock Generator locks on to this incoming rate and multiplies the word rate clock by 20 (16 word bits + 4 encoding bits). As lock is achieved, LOCKED is set high. The TXDIV1/0 pins configure the transmitter to accept incoming data words within the desired frequency range.

By setting TCLKENB high, the user may provide an external TTL high speed serial clock at TXCLK. This clock replaces the internal VCO clock and is intended for diagnostic purposes only. This uncharacterized signal is used directly by the high-speed serial circuitry to output the serial data at speeds that are not within the VCO range.

# C-Field and W-Field Encoder Logic

This logic determines what information is sent to the encoded word mux. If TXCNTL is high, the logic sends bits TX[0-13] and a C-Field (coding field) encoded as a control word regardless of the state of TXDATA. If TXCNTL is low and TXDATA is high, the logic sends TX[0-15] and a C-Field encoded as a data word. If neither TXCNTL nor TXDATA is set high, then the transmitter assumes the link is not being used. In this case, the logic submits an Idle Word to the encoded word mux to maintain the DC balance on the serial link and allow the receiver to maintain frequency and phase lock.

The C-Field logic, based on the inputs at TXCNTL, TXDATA, TXFLGENB and TXFLAG, supplies the four bits of the C-field to the encoded word mux. These bits contain information regarding the word type: Control, Data or Idle. In order for the TXFLAG bit to be used as an additional data bit, TXFLGENB must be set high on the Tx and RXFLGENB must be set high on the Rx. If scrambling of the encoding of the flag bit is desired, ESMPXENB pin must be set high on both the Tx and Rx. See Flag Descrambler section on next page for a more detailed description of the enhanced simplex mode.

The W-Field logic (word field) presents either bits TX[0-15] or an Idle Word to the encoded word mux.

#### **Encoded Word Mux**

The Word Mux accepts the four encoding bits from the C-Field and 16 data bits from the W-Field. These 20 bits of parallel information are then multiplexed to a serial line based on the internal high-speed serial clock.

Figure 3. HDMP-1032A Transmitter Block Diagram.

# Sign

The sign circuitry determines the disparity of the encoded word. Disparity is defined as the total number of high bits minus the total number of low bits.

# **Accumulator Block**

This block is responsible for keeping track of total disparity of all previously sent words.

#### **Invert Block**

The Invert block is responsible for maintaining the DC balance of the serial line. It determines based on history and the sign of the current encoded word whether the current encoded word should be inverted to bring the serial line closer to the desired 50% duty cycle.

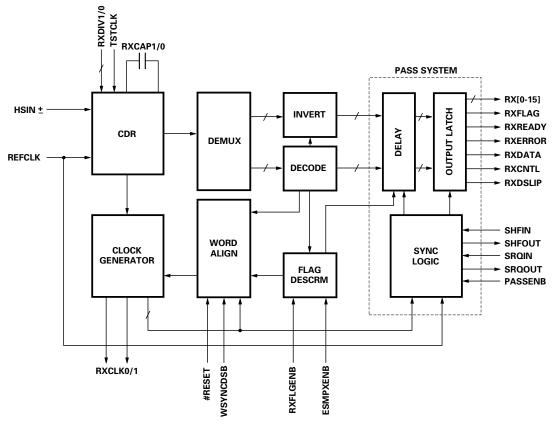

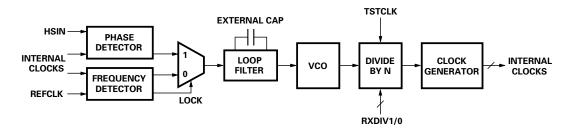

#### HDMP-1034A Rx Block Diagram

The HDMP-1034A receiver was designed to convert a serial data signal sent from the HDMP-1032A into either 16 or 17 bit wide parallel data. The HDMP-1034A performs the following functions:

- Frequency Lock

- Phase Lock

- Encoded Word Synchronization

- De-multiplexing

- Word Decoding

- Encoding Error Detection

# Input Sampler and Clock-Data Recovery (CDR)

In order to compensate for any amplitude distortion present in the serial data signal, the highspeed inputs,  $HSIN\pm$ , are always equalized. The CDR block locks to the frequency of the REFCLK and to the phase of the sampled input signal. The recovered data is sent to the DEMUX block and a bit-rate clock is sent to the Clock Generator block. If the serial data signal is absent, the CDR block will maintain frequency lock onto REFCLK. The RXDIV1/0 pins select the data rate range by dividing the VCO range by 1, 2 or 4. When RXDIV1/0 = 1/1, the internal VCO is bypassed and the test clock input TSTCLK can be used as the serial input.

#### **Clock Generator**

Using the recovered bit-rate clock, the CLOCK GENERATOR block generates all of the required internal clocks including the word rate clocks: RXCLK0/1.

Using the WORD ALIGN block's bit adjust output, the phase of the word-rate clocks is adjusted bit by bit for proper word alignment. For testing purposes this adjustment function can be disabled using the WSYNCDSB input; word alignment can also be forced using the #RESET pin.

Figure 4. HDMP-1034A Receiver Block Diagram.

# **Demultiplexer (DEMUX)**

This block takes the recovered serial data from the CDR block and demultiplexes it into a 20-bit parallel word comprised of a 16-bit word-field and 4-bit code-field.

# Decoder (DECODE)

This block decodes the 4-bit code-field and determines whether the 16-bit word-field is: normal or inverted; data, control, or idle words; or errors. The flag bit is also decoded from the data word.

#### Word Alignment (WORD ALIGN)

This block detects the error output of the decoder block. Upon detecting two consecutive errors, WORD ALIGN requests a bit adjustment to the clock generator (assuming WSYNCDSB=0).

If enhanced simplex mode is engaged (ESMPXENB=1), the Word Align block looks for a transition in the scrambled flag bit over a window of 32 words. If a transition is not detected, WORD ALIGN requests a bit adjustment to the clock generator (assuming WSYNCDSB=0).

When the bit adjustment output has been low for 64 up to 128 words, the RXREADY output goes high. If the bit adjustment output goes high, RXREADY immediately goes low.

# Flag Descrambler (FLAG DESCRM)

This block descrambles the flag bit if the enhanced simplex mode is engaged (ESMPXENB=1); otherwise, the flag bit is unaltered. Scrambling ensures that the flag bit is dynamic and thus can be detected by the word alignment block. Scrambling of the flag bit provides an extra level of protection to guard against improper word alignment caused by static valid code-field bits being embedded within the data-field.

Enhanced simplex mode can be turned off (ESMPXENB=0) to make it compatible with previous versions of G-Link. With this mode turned off and TXFLGENB=1, the flag bit is sent unscrambled to the Rx. If TXFLGENB=0, the flag bit will alternate at the Tx. When RXFLGENB=0, the Rx will use this alternating flag for error checking.

# Parallel Automatic Synchronization System (Pass)

As shown in Figure 4, this system consists of three blocks: the parallel delay block (DELAY), the output latch block (OUTPUT LATCH), and the synchronization logic block (SYNC LOGIC). This system was designed to provide a simple interface to the parallel outputs for a synchronous system.

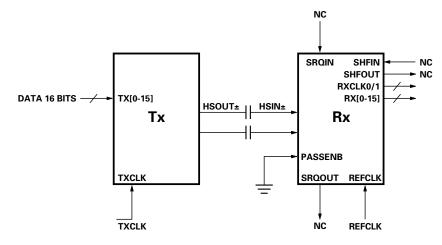

# Background

Traditionally, the parallel outputs are clocked out with the falling edge of RXCLK1 as shown in Figure 4.1. Since this clock is recovered from the serial data, this clock is synchronous with the remote clock at the Tx. When the Tx and Rx clock are not synchronous, FIFO's are usually used to cross the frequency domains. The size of the FIFO and the frequency difference determine the maximum packet size of transmission.

When the clock from the Tx is synchronous with the Rx clock. data can be transmitted continuously without FIFO's since the parallel output data is synchronous with the local REFCLK. However, due to link distance and other physical variables, the relative phase of the REFCLK to the recovered data is unpredictable. Because of this unknown phase, the sampling of the recovered word must be adjusted so that the internal setup/hold times are not violated. Furthermore, in a multichannel system, the setting of the phase must be consistent so that time slots across the channels are preserved.

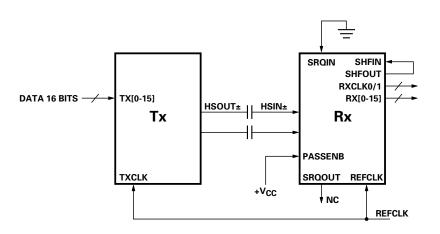

The PASS system was designed to address these issues by sensing the phase difference between the local REFCLK with the recovered clock, and shifts the phase of the parallel output data with the DELAY block, such that it can be clocked out with the rising edge

Figure 4.1. Traditional G-Link configuration with PASS disabled (PASSENB=0). Recovered data words and RXCLK0/1 are synchronous with TXCLK.

of the REFCLK. By adjusting the phase of the data word rather than REFCLK, the optimal setup time is achieved for the input latches of the chip interfacing to the Rx.

As the relative phase between the HSIN± input and the REFCLK drift slowly over time due to environmental variations, the PASS system is able to absorb this to some degree, and is able to reset and re-optimize the sampling when the margin is exceeded.

# **DELAY Block**

The parallel DELAY block has an adjustable delay range of 20% to 80% of the data word. Its delay is controlled by the SYNC LOGIC block. This delay block is used for all of the data bits, flag bit, as well as the status bits.

# **OUTPUT LATCH Block**

This block is a bank of positive edge triggered D-flip/flops. The clock is selected by the SYNC LOGIC block to be either the recovered clock RXCLK1 when the PASS system is disabled, or the REFCLK when the PASS system is enabled (PASSENB=1).

# SYNC LOGIC Block

The SYNC LOGIC block's function is to compare the phase of the recovered data to REFCLK, to set the state of the DELAY block, to detect when the DELAY range has been exceeded, and to recover with a new DELAY setting. It is also designed to support a master/slave configuration in a multi-channel environment. When RXREADY goes high, the optimal delay choice is determined at the shift output SHFOUT: SHFOUT = 0 DELAY retract SHFOUT = 1 DELAY extend

The actual setting of the DELAY block is determined with the shift input SHFIN.

When the phase of the REFCLK drifts to within 10% of the word boundary, the RXDSLIP output is set high, and a new choice of SHFOUT is chosen. The shift request output SQROUT is set high when a RXDSLIP condition is detected, or if the shift request input SRQIN goes high.

#### **Single Channel Configuration**

In a single channel configuration, SHFIN is simply tied to SHFOUT as shown in Figure 4.2. The daisy chaining signal SRQIN is set low (grounded) and SRQOUT is left unconnected.

After RXREADY goes high, the DELAY block can absorb a phase variation between the serial input HSIN $\pm$  and the REFCLK a minimum of ideally  $\pm$  4 serial bits, or 20% of the word period. This margin is reduced due to finite rise/fall times and setup times of the internal circuitry.

Figure 4.2. Single channel configuration with PASS enabled (PASSENB=1). Recovered data words and RXCLK0/1 are synchronous with REFCLK.

#### **Multiple Channel Configuration**

The connections for a multiple channel configuration are shown in Figure 4.3. The daisy-chain signals SRQIN and SRQOUT are used to allow each receiver's PASS system shift requests to propagate to the master, which is the last of the chain. The master then controls the shift command SHFOUT, which is tied common to the SHFIN of each receiver. The first SRQIN in the chain is grounded; the SRQOUT of the master as well as the SHFOUT outputs of the slave units are left unconnected.

When the internal parallel data boundary of the master, or any of the slaves come within 10% of the REFCLK, the RXDSLIP output is set high by the respective Rx, a shift request (SRQOUT=1) is issued which propagates to the master. The master again selects an optimum SHFOUT, which sets the DELAY blocks of all receivers consistently.

The phase absorption margin for a multiple channel configuration is the same as the single channel case, less the channel-to-channel skews.

Figure 4.3. Multiple channel configuration with PASS Enabled (PASSENB=1).

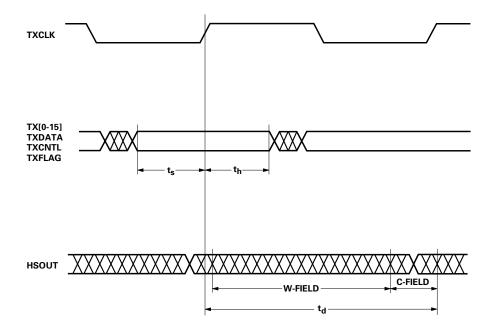

#### HDMP-1032A (Tx) Timing

The Tx timing diagram is shown in Figure 5. Under normal operations, the Tx PLL locks an internally generated clock to the incoming TXCLK at which time LOCKED is set high. The incoming data, TX[0-15], TXDATA, TXCNTL, and TXFLAG are latched by this internal clock. The data must be valid for  $t_s$ before it is sampled and remain valid for a time  $t_h$  after it is sampled. The setup and hold time parameters,  $t_s$  and  $t_h$ , are referenced to the rising edge of TXCLK.

The start of a word, bit TX[0], in the high speed serial output occurs after a delay of  $t_d$  after the rising edge of the TXCLK. The typical value of  $t_d$  is approximately one clock cycle.

# HDMP-1032A (Tx) Timing Characteristics

Tc =  $-20^{\circ}C$  to +85°C,  $V_{CC}$  = 3.15V to 3.45V

| Symbol         | Parameter                                                                                | Unit | Min. | Тур. | Max. |

|----------------|------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>s</sub> | Setup Time, for TX[0-15], TXDATA, TXCNTL and<br>TXFLAG Relative to Rising Edge of TXCLK. | nsec | 2.5  |      |      |

| t <sub>h</sub> | Hold Time, for TX[0-15], TXDATA, TXCNTL and<br>TXFLAG Relative to Rising Edge of TXCLK.  | nsec | 2.5  |      |      |

Figure 5. HDMP-1032A (Tx) Timing Diagram.

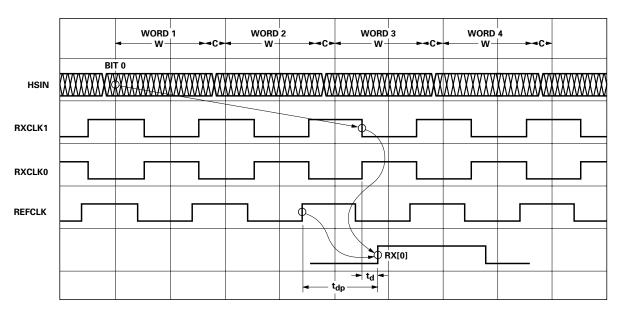

#### HDMP-1034A (Rx) Timing

The Rx timing diagram when RXREADY=1 is shown in Figure 6. The serial data stream is deserialized into a parallel word at 1/20 the serial baud rate.

When the PASS system is disabled (PASSENB=0), there is a latency delay of two words from the input of the first serial bit of a word to the parallel outputs. The parallel outputs, RX[0-15], RXFLAG, RXREADY, RXERROR, RXDATA, RXCNTL and RXDSLIP are clocked out with the falling edge of RXCLK1 and appear after a delay of t<sub>d</sub>. RXCLK1 and its complement RXCLK0 are both 50% duty cycle clocks.

When the PASS system is enabled (PASSENB=1), the timing of the parallel word is adjusted automatically  $\pm$  30% of the word period so that it can be clocked out with the rising edge of REFCLK and appear after a delay of t<sub>dp</sub>.

# HDMP-1034A (Rx) Timing Characteristics

Tc =  $-20^{\circ}$ C to  $+85^{\circ}$ C, V<sub>CC</sub> = 3.15V to 3.45V. Typical values are at Tc =  $25^{\circ}$ C, V<sub>CC</sub> = 3.3V

| Symbol          | Parameter                                                                                            | Unit | Min. | Тур. | Max.                            |

|-----------------|------------------------------------------------------------------------------------------------------|------|------|------|---------------------------------|

| t <sub>d</sub>  | Synchronous Output Delay referenced to the falling edge of RXCLK1, PASS System Disabled (PASSENB=0). | nsec | 0    | 2.0  | 3.5                             |

| t <sub>dp</sub> | Synchronous Output Delay referenced to the rising edge of REFCLK, PASS System Enabled (PASSENB=1).   | nsec | 6.0  | 6.6  | 8.0                             |

| t <sub>sk</sub> | Allowable skew between HSIN and REFCLK before PASS system resets, PASSENB=1.                         | nsec |      |      | 20% word<br>period<br>-0.4 nsec |

NOTE: W = 16 BIT WORD FIELD, C = 4 BIT CODE FIELD

Figure 6. HDMP-1034A (Rx) Timing Diagram.

# HDMP-1032A (Tx), HDMP-1034A (Rx)

**DC Electrical Specifications**

| Symbol              | Parameter                                                                             | Unit | Min. | Тур. | Max.            |

|---------------------|---------------------------------------------------------------------------------------|------|------|------|-----------------|

| V <sub>IH,TTL</sub> | TTL Input High Voltage Level, Guaranteed high signal for all inputs.                  | V    | 2.0  |      | V <sub>CC</sub> |

| V <sub>IL,TTL</sub> | TTL Input Low Voltage Level, Guaranteed low signal for all inputs.                    | V    | 0    |      | 0.8             |

| V <sub>OH,TTL</sub> | TTL Output High Voltage Level, I <sub>0H</sub> = -400 μA                              | V    | 2.2  |      | V <sub>CC</sub> |

| V <sub>OL,TTL</sub> | TTL Output Low Voltage Level, $I_{\text{OL}}$ = 500 $\mu\text{A}$                     | V    | 0    |      | 0.6             |

| I <sub>IH,TTL</sub> | Input High Current, V <sub>IN</sub> = V <sub>CC</sub>                                 | μΑ   |      |      | 40              |

| I <sub>IL,TTL</sub> | Input Low Current, V <sub>IN</sub> = 0 volts                                          | μA   |      |      | 600             |

| V <sub>IP,H50</sub> | H50 Input Peak-To-Peak Differential Voltage                                           | mV   | 200  |      |                 |

| V <sub>OP,BLL</sub> | BLL Output Peak-To-Peak Differential Voltage, Terminated with 50 $\Omega,$ ac coupled | mV   | 1000 |      |                 |

| I <sub>CC,Tx</sub>  | Transmitter V <sub>CC</sub> Supply Current                                            | mA   |      | 200  |                 |

| I <sub>CC,Rx</sub>  | Receiver V <sub>CC</sub> Supply Current                                               | mA   |      | 240  |                 |

Tc =  $-20^{\circ}$ C to  $+85^{\circ}$ C, V<sub>CC</sub> = 3.15V to 3.45V, Typical values are at Tc =  $25^{\circ}$ C, V<sub>CC</sub> = 3.3V

# **AC Electrical Specifications**

Tc = 25°C

| Symbol                 | Parameter                                                                  | Unit  | Min. | Тур. | Max |

|------------------------|----------------------------------------------------------------------------|-------|------|------|-----|

| t <sub>r,TTL in</sub>  | Input TTL Rise Time, 0.8 to 2.0 volts                                      | nsec  |      | 2    |     |

| tf,TTL in              | Input TTL Fall Time, 2.0 to 0.8 volts                                      | nsec  |      | 2    |     |

| t <sub>r,TTL out</sub> | Output TTL Rise time, 0.8 to 2.0 volts, 10 pF load                         | nsec  |      |      | 3.0 |

| t <sub>f,TTL out</sub> | Output TTL Fall Time, 2.0 to 0.8 volts, 10 pF load                         | nsec  |      |      | 3.0 |

| t <sub>r,BLL</sub>     | BLL Rise Time, Terminated with 50, ac coupled <sup>1</sup>                 | psec  |      | 240  |     |

| t <sub>f,BLL</sub>     | BLL Fall Time, Terminated with 50, ac coupled <sup>1</sup>                 | psec  |      | 240  |     |

| VSWR <sub>i,H50</sub>  | H50 Input VSWR                                                             |       |      | 2:1  |     |

| VSWR <sub>o,BLL</sub>  | BLL Output VSWR                                                            |       |      | 2:1  |     |

| t <sub>fa</sub>        | Transmitter & Receiver Frequency Acquisition Time at Power-on <sup>2</sup> | msec  |      | 4    |     |

| t <sub>Rx_wa</sub>     | Receiver Word Alignment Time                                               | Words |      | 300  |     |

Notes

1. Rise and fall times are measured between 20% and 80% of the voltage range.

2. Frequency acquisition time is independent of DIV1/DIV0 data rate range.

**Latency** Tc = 25°C

|      | Lat<br>Word Clo | ency<br>ck Cycles) | Latency Definition                                                                                                                                        |

|------|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | PASSENB = 0     | PASSENB = 1        |                                                                                                                                                           |

| Тх   | 1.4             | 1.4                | Delay from the rising edge of TXCLK to the first bit TX[0] in the serial stream                                                                           |

| Rx   | 2.6             | 3.0                | Delay from the first bit RX[0] in the serial stream to the falling edge of RXCLK1 (or the rising edge of REFCLK if the PASS system is enabled, PASSENB=1) |

| Link | 4.0             | 4.4                |                                                                                                                                                           |

# Transmit Word Clock (TXCLK) and Receiver Reference Clock (REFCLK) Requirements

Tc =  $-20^{\circ}$ C to  $+85^{\circ}$ C, V<sub>CC</sub> = 3.15 V to 3.45 V

| Symbol           | Parameter                                                               | Unit | Min. | Тур. | Max. |

|------------------|-------------------------------------------------------------------------|------|------|------|------|

| F <sub>tol</sub> | TXCLK and REFCLK Frequency Tolerance<br>(REFCLK is referenced to TXCLK) | ppm  | -100 |      | +100 |

| Symm             | Symmetry (Duty Cycle)                                                   | %    | 40   |      | 60   |

# HDMP-1032A (Tx), HDMP-1034A (Rx)

# Absolute Maximum Ratings

$T_A = 25^{\circ}C$  except as specified. Operation in excess of any one of these conditions may result in permanent damage to the device.

| Symbol              | Parameter                                         | Unit | Min. | Max.            |

|---------------------|---------------------------------------------------|------|------|-----------------|

| V <sub>CC</sub>     | Supply Voltage                                    | V    | -0.5 | 5.0             |

| V <sub>IN,TTL</sub> | TTL Input Voltage                                 | V    | -0.7 | 5.5             |

| V <sub>IN,BLL</sub> | H50 Input Voltage                                 | V    | 2.0  | V <sub>CC</sub> |

| I <sub>0,TTL</sub>  | TTL Output Source Current                         | mA   |      | 13              |

| T <sub>stg</sub>    | Storage Temperature                               | °C   | -65  | +150            |

| TJ                  | Junction Temperature                              | °C   | 0    | +150            |

| T <sub>max</sub>    | Maximum Assembly Temperature (10 seconds maximum) | °C   |      | +260            |

# HDMP-1032A (Tx) Thermal Characteristics

$T_A = 25^{\circ}C$

| Symbol            | Parameter                                  | Unit | Тур. |

|-------------------|--------------------------------------------|------|------|

| θ <sub>jc</sub> 1 | Thermal Resistance, Die to Case            | °C/W | 8    |

| PD                | Power Dissipation, V <sub>CC</sub> = 3.3 V | mW   | 660  |

# HDMP-1034A (Rx) Thermal Characteristics

$T_A=25^\circ C$

| Symbol            | Parameter                           | Unit | Тур. |

|-------------------|-------------------------------------|------|------|

| θ <sub>jc</sub> 1 | Thermal Resistance, Die to Case     | °C/W | 8    |

| PD                | Power Dissipation, $V_{CC} = 3.3 V$ | mW   | 792  |

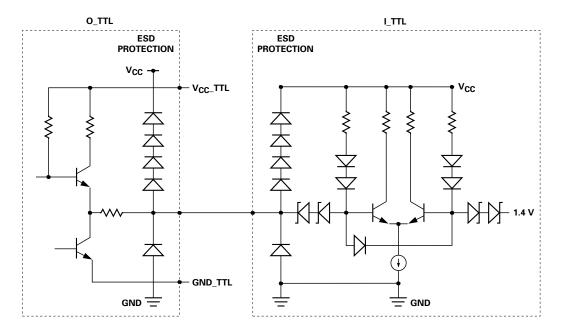

# I/O Type Definitions

| I/O Type | Definition                                                                                                                                               |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| I-TTL    | Input TTL. Floats high when left open.                                                                                                                   |

| 0-TTL    | Output TTL                                                                                                                                               |

| HS_OUT   | 50 $\Omega$ Matched Output Driver. Will drive AC coupled 50 $\Omega$ loads. All unused outputs should be AC coupled to a 50 $\Omega$ resistor to ground. |

| HS IN    | High Speed Input                                                                                                                                         |

| С        | Filter Capacitor Node                                                                                                                                    |

| S        | Power Supply or Ground                                                                                                                                   |

Note:

Based on independent package testing by HP. θ<sub>ja</sub> for the HDMP-1032A and HDMP-1034A is 50°C/W. θ<sub>ja</sub> is measured on a standard 3" x 3" two layer PCB in a still air environment. In order to determine the actual junction temperature in a given application, use the following formula:  $T_J = T_C + (\theta_{jc} \times P_D)$ , where  $T_C$  is the case temperature measured on the top center of the package and  $P_D$  is the power being dissipated.

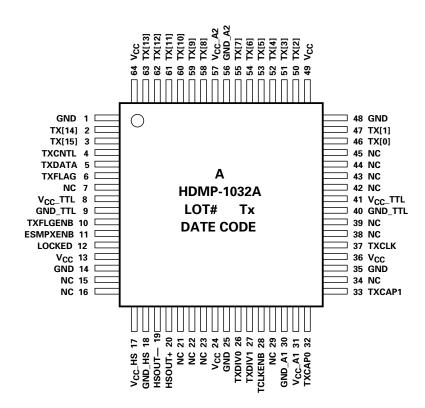

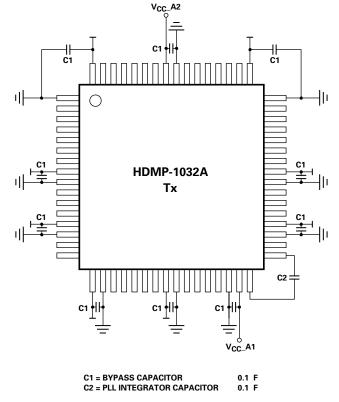

Figure 7. HDMP-1032A (Tx) Package Layout, Top View.

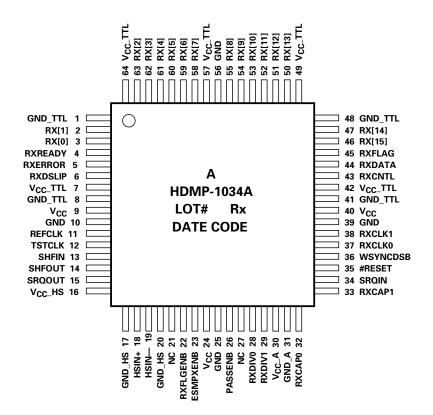

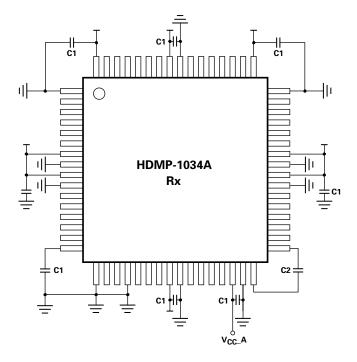

Figure 8. HDMP-1034A (Rx) Package Layout, Top View.

# HDMP-1032A (Tx) Pin Definition

| User Mode Op<br>Name                                                                                                                                         | Pin                                                                                        | Туре          | Signal                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| TXFLGENB                                                                                                                                                     | 10                                                                                         | Type<br>I-TTL | Flag Bit Mode Select: When this input is high, the TXFLAG bit<br>input is sent as an extra 17th data bit during data word transfers.<br>As an example, the flag bit can be used as an even or odd word<br>indicator for 32 bit transmission. The RXFLGENB input on the Rx<br>chip must be set to the same value as the TXFLGENB pin.                                      |  |  |  |  |  |  |  |

| ESMPXENB                                                                                                                                                     | 11                                                                                         | I-TTL         | <b>Enhanced Simplex Mode Enable:</b> Enables scrambling of the Flag<br>Bit encoding. The ESMPXENB pin on the Rx chip must be set to<br>the same value. This mode should be enabled unless compatibility<br>with previous versions of G-Link (i.e. HDMP-1024/1014) is desired<br>desired which don't have this feature.                                                    |  |  |  |  |  |  |  |

| TXDATA                                                                                                                                                       | 5                                                                                          | I-TTL         | <b>Transmit Data Word:</b> This input tells the chip that the user has valid data to be transmitted. When this pin is asserted and TXCNTL is low, bits TX[0-15] and optionally TXFLAG are encoded and sent as a data word.                                                                                                                                                |  |  |  |  |  |  |  |

| TXCNTL                                                                                                                                                       | 4                                                                                          | I-TTL         | <b>Transmit Control Word:</b> This input tells the Tx chip that the user<br>is requesting a control word to be transmitted. When this pin is<br>asserted, bits TX[0-13] are sent as a control word. If TXCNTL and<br>TXDATA are asserted simultaneously, TXCNTL takes precedence.<br>Idle words are transmitted if both TXDATA and TXCNTL are low.                        |  |  |  |  |  |  |  |

| High-Speed S                                                                                                                                                 | erial/Par                                                                                  | allel I/O     |                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

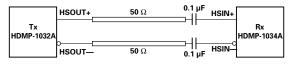

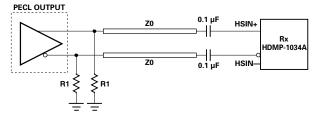

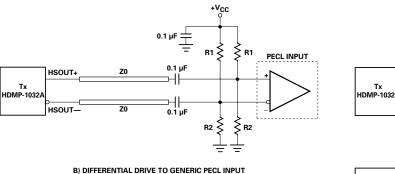

| HSOUT+<br>HSOUT-                                                                                                                                             | 20<br>19                                                                                   | HS_OUT        | Serial Data Output: These pins form a buffer line logic driver, which is a 50 $\Omega$ terminated PECL compatible output.                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| TX[0]<br>TX[1]<br>TX[2]<br>TX[3]<br>TX[4]<br>TX[5]<br>TX[6]<br>TX[7]<br>TX[8]<br>TX[9]<br>TX[10]<br>TX[10]<br>TX[11]<br>TX[12]<br>TX[13]<br>TX[14]<br>TX[15] | 46<br>47<br>50<br>51<br>52<br>53<br>54<br>55<br>58<br>59<br>60<br>61<br>62<br>63<br>2<br>3 | I-TTL         | <b>Word Inputs</b> : When sending data words, TX[0-15] are serialized.<br>When sending control words, TX[0-13] are serialized.                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| TXFLAG                                                                                                                                                       | 6                                                                                          | I-TTL         | <b>Flag Bit:</b> When TXFLGENB is active, this input is sent as an extra data bit in addition to the 16 data word bits. When TXFLGENB is not asserted, this input is ignored and an alternating internal flag bit is transmitted to allow the Rx chip to perform error detection during data word transfers. The Flag Bit is not sent when a control word is transmitted. |  |  |  |  |  |  |  |

# HDMP-1032A (Tx) Pin Definition (continued)

| PLL/Clock Ge                               | enerator                                                                        |       |                                                                                                                                                                                                                                              |

|--------------------------------------------|---------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                       | Pin                                                                             | Туре  | Signal                                                                                                                                                                                                                                       |

| TXCAP0<br>TXCAP1                           | 32<br>33                                                                        | С     | <b>Loop Filter Capacitor:</b> A 0.1 $\mu$ F min. loop filter capacitor, C2, must be connected across TXCAP0 and TXCAP1 for all combinations of TXDIV1/TXDIV0. See Figure 12.                                                                 |

| TXCLK                                      | 37                                                                              | I-TTL | <b>Transmit Word Clock Input:</b> When TCLKENB is low, this word rate clock input is phase locked and multiplied to generate the high-speed serial clock. When TCLKENB is high, the PLL is bypassed and TXCLK becomes the serial clock.      |

| TXDIV0<br>TXDIV1                           | 26<br>27                                                                        | I-TTL | VCO Divider Select: These pins program the VCO divider chain to operate at full, half or quarter speed. See Typical Operating Rates table and Figure 2.                                                                                      |

| LOCKED                                     | 12                                                                              | 0-TTL | Locked to TXCLK: This pin goes high when the transmit PLL achieves frequency lock to the TXCLK signal.                                                                                                                                       |

| Power Suppl                                | y/Ground                                                                        |       |                                                                                                                                                                                                                                              |

| V <sub>CC</sub>                            | 13<br>24<br>36<br>49<br>64                                                      | S     | <b>Logic Power Supply</b> : Normally 3.3 volts. This power supply is used for the internal transmitter logic.                                                                                                                                |

| V <sub>CC</sub> _TTL                       | 8<br>41                                                                         | S     | <b>TTL Power Supply:</b> Normally 3.3 volts. Used for all TTL transmitter input and output buffer cells.                                                                                                                                     |

| V <sub>CC</sub> _HS                        | 17                                                                              | S     | Serial Output Power Supply: Normally 3.3 volts. Used for Serial Output pins.                                                                                                                                                                 |

| V <sub>CC</sub> _A1<br>V <sub>CC</sub> _A2 | 31<br>57                                                                        | S     | Analog Power Supply: Normally 3.3 volts. Used for the analog section.                                                                                                                                                                        |

| GND                                        | 1<br>14<br>25<br>35<br>48                                                       | S     | <b>Ground</b> : Normally 0 volts. Tie to ground.                                                                                                                                                                                             |

| GND_TTL                                    | 9<br>40                                                                         | S     | TTL Ground: Normally 0 volts. Tie to ground.                                                                                                                                                                                                 |

| GND_HS                                     | 18                                                                              | S     | Serial Output Ground: Normally 0 volts.                                                                                                                                                                                                      |

| GND_A1<br>GND_A2                           | 30<br>56                                                                        | S     | Analog Ground: Normally 0 volts.                                                                                                                                                                                                             |

| Test Mode/N                                | lo Connect I                                                                    | Pins  |                                                                                                                                                                                                                                              |

| TCLKENB                                    | 28                                                                              | I-TTL | <b>Enable External Serial Rate Clock Input</b> : When set high, this input causes the TXCLK input to be used for the serial transmit clock rather than the internal VCO clock. It is intended for diagnostic purposes and normally tied low. |

| NC                                         | 7<br>15<br>16<br>21<br>22<br>23<br>29<br>34<br>38<br>39<br>42<br>43<br>44<br>45 |       | <b>No Connect:</b> These pins should be left unconnected.                                                                                                                                                                                    |

# HDMP-1034A (Rx) Pin Definition

| User Mode Op                                                                                                                                                           | tions/Sta                                                                                        | itus           |                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                                                                                                                                   | Pin                                                                                              | Туре           | Signal                                                                                                                                                                                                                                                                                                                                                                             |

| RXFLGENB                                                                                                                                                               | 22                                                                                               | I-TTL          | Flag Bit Mode Select: When set high, the RXFLAG bit output is available to the user as an extra 17th data bit.                                                                                                                                                                                                                                                                     |

| ESMPXENB                                                                                                                                                               | 23                                                                                               | I-TTL          | <b>Enhanced Simplex Mode Enable:</b> Enables descrambling of the Flag<br>Bit encoding. The ESMPXENB pin on the Tx chip must be set to the<br>same value. This mode should be enabled unless compatibility with<br>previous versions of G-Link (i.e. HDMP-1022/1012) is desired which<br>don't have this feature.                                                                   |

| PASSENB                                                                                                                                                                | 26                                                                                               | I-TTL          | <b>Enable Parallel Automatic Synchronization System:</b> The parallel Rx data and control words are read out with REFCLK instead of the incoming word's parallel clock. The relative phase of the parallel output bits is internally adjusted so that they are clocked out with the rising edge of the REFCLK.                                                                     |

| RXDATA                                                                                                                                                                 | 44                                                                                               | 0-TTL          | <b>Data Word Available Output:</b> This output indicates that the Rx chip word outputs RX[0-15] have a data word.                                                                                                                                                                                                                                                                  |

| RXCNTL                                                                                                                                                                 | 43                                                                                               | 0-TTL          | <b>Control Word Available Output:</b> This output indicates that the Rx chip word outputs RX[0-13] have a control word.                                                                                                                                                                                                                                                            |

| High-Speed S                                                                                                                                                           | erial/Para                                                                                       | allel I/O      |                                                                                                                                                                                                                                                                                                                                                                                    |

| HSIN+<br>HSIN-                                                                                                                                                         | 18<br>19                                                                                         | HS_IN          | Serial Data Input                                                                                                                                                                                                                                                                                                                                                                  |

| RX[0]<br>RX[1]<br>RX[2]<br>RX[3]<br>RX[4]<br>RX[5]<br>RX[6]<br>RX[7]<br>RX[8]<br>RX[9]<br>RX[10]<br>RX[10]<br>RX[11]<br>RX[12]<br>RX[13]<br>RX[14]<br>RX[15]<br>RXFLAG | 3<br>2<br>63<br>62<br>61<br>60<br>59<br>58<br>55<br>54<br>53<br>52<br>51<br>50<br>47<br>46<br>45 | 0-TTL<br>0-TTL | Word Outputs Flag Bit: If both TXFLGENB and RXFLGENB have been asserted, this output indicates the value of the transmitted flag bit which can be used as an extra 17th data bit.                                                                                                                                                                                                  |

| Link Status                                                                                                                                                            |                                                                                                  |                |                                                                                                                                                                                                                                                                                                                                                                                    |

| RXREADY                                                                                                                                                                | 4                                                                                                | 0-TTL          | <b>Receiver Ready:</b> This signal is asserted when the word alignment<br>block has seen error-free code field nibbles for 64 up to 128<br>consecutive words. When ESMPXENB = 1, the toggling of the<br>scrambled flag bit is also checked. RXREADY is de-asserted<br>upon 2 consecutive errors in the code field or if the toggling of<br>the flag bit is absent when ESMPXENB=1. |

| RXERROR                                                                                                                                                                | 5                                                                                                | 0-TTL          | <b>Received Data Error:</b> Asserted when a word is received which does not correspond to either a valid Data, Control, or Idle Word encoding.                                                                                                                                                                                                                                     |

# HDMP-1034A (Rx) Pin Definition (continued)

| CDR/Clock G          |                           |       |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|----------------------|---------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Name                 | Pin                       | Туре  | Signal                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| RXCAP0<br>RXCAP1     | 32<br>33                  | С     | <b>Loop Filter Capacitor:</b> A 0.1 μF min. loop filter capacitor, C2, must be connected across RXCAP0 and RXCAP1 for all combinations of RXDIV1/RXDIV0. See Figure 12.                                                                                                 |  |  |  |  |  |  |  |  |

| REFCLK               | 11                        | I-TTL | <b>Reference Clock Input:</b> The Rx PLL uses this input for frequency lock. In addition, RX[0-15], RXFLAG, RXDATA, RXCNTL, RXREADY, RXERROR, and RXDSLIP are clocked out on the rising edge of REFCLK when PASSENB=1.                                                  |  |  |  |  |  |  |  |  |

| RXDIV0<br>RXDIV1     | 28<br>29                  | I-TTL | <b>VCO Divider Select:</b> These pins program the VCO divider chain to operate at full, half, or quarter speed. See Typical Operating Rates table and Figure 2.                                                                                                         |  |  |  |  |  |  |  |  |

| RXCLK0<br>RXCLK1     | 37<br>38                  | 0-TTL | <b>Recovered Word-Rate Clock Outputs:</b> These outputs are the PLL recovered word rate clocks. RX[0-15], RXFLAG, RXDATA, RXCNTL, RXREADY, RXERROR, and RXDSLIP are clocked out on the falling edge of RXCLK1 when PASSENB=0. RXCLK0 is the inverse of RXCLK1.          |  |  |  |  |  |  |  |  |

| Power Supply         | y/Ground                  |       |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| V <sub>CC</sub>      | 9<br>24<br>40             | S     | <b>Power Supply:</b> Normally 3.3 volts. This power supply is used for all the core logic other than the output drivers.                                                                                                                                                |  |  |  |  |  |  |  |  |

| V <sub>CC</sub> _TTL | 7<br>42<br>49<br>57<br>64 | S     | <b>TTL Power Supply:</b> Normally 3.3 volts. Used for all TTL receiver input and output buffer cells.                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| V <sub>CC</sub> HS   | 16                        | S     | <b>High-Speed Supply:</b> Normally 3.3 volts. This supply is used to provide clean references for the high-speed inputs, HSIN+ and HSIN                                                                                                                                 |  |  |  |  |  |  |  |  |

| V <sub>CC</sub> A    | 30                        | S     | <b>Analog Power Supply:</b> Normally 3.3 volts. This supply is used to feed power to the analog section of the chip.                                                                                                                                                    |  |  |  |  |  |  |  |  |

| GND                  | 10<br>25<br>39<br>56      | S     | <b>Ground:</b> Normally 0 volts. Tie to ground.                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| GND_TTL              | 1<br>8<br>41<br>48        | S     | TTL Ground: Normally 0 volts. Tie to ground.                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

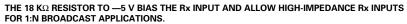

| GND_HS               | 17<br>20                  | S     | <b>High-Speed Input Ground:</b> When tied to ground, the input impedance of HSIN+ and HSIN- are each matched to 50 $\Omega$ . In order to obtain high impedance (high-Z) inputs for 1:N broadcast applications, 18 K $\Omega$ series resistors to -5 V are recommended. |  |  |  |  |  |  |  |  |

| GND_A                | 31                        | S     | Analog Ground: Normally 0 volts. This ground is used for the analog PLL portion of the chip.                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| HDMP-1034A | (Rx) Pin | Definition | (continued) |

|------------|----------|------------|-------------|

|------------|----------|------------|-------------|

| Pass System  |          |       |                                                                                                                                                                                                                                                                         |

|--------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDSLIP      | 6        | 0-TTL | <b>Rx Word Slip:</b> This output is asserted whenever the phase of the parallel word relative to the reference clock has exceeded the range of the internal delay, which results in a slippage of one word. See discussion of PASS system on page 7.                    |

| SHFIN        | 13       | I-TTL | <b>Shift Input:</b> This input controls the delay of the parallel bits to be clocked out by REFCLK when PASSENB=1. In a single Rx configuration, SHFIN is connected to SHFOUT. In a multiple Rx configuration, all SHFIN are connected to the master's SHFOUT.          |

| SHFOUT       | 14       | 0-TTL | <b>Shift Output:</b> This output, normally connected to SHFIN, is generated based on the relative phase between REFCLK and the internal parallel output bits.                                                                                                           |

| SRQIN        | 34       | I-TTL | <b>Shift Request Input:</b> In a daisy chain configuration, this input<br>allows a shift request to be propagated to the master. SRQIN is<br>connected to the SRQOUT of the previous Rx in a multi-receiver<br>configuration.                                           |

| SRQOUT       | 15       | 0-TTL | <b>Shift Request Output:</b> In a daisy chain configuration, this output<br>is connected to the SRQIN input of the next receiver. SRQOUT<br>goes high when a SRQIN=1 or when the relative phase between<br>the REFCLK and the internal parallel bits requires a shift.  |

| Test Mode/No | Connect  | Pins  |                                                                                                                                                                                                                                                                         |

| TSTCLK       | 12       | I-TTL | <b>External Serial Rate Clock Input</b> : When RXDIV1/0 = 1/1, this input is used in place of the normal VCO signal, effectively disabling the PLL and allowing the user to provide an external serial clock for testing. Pin is normally tied to V <sub>CC</sub> _TTL. |

| #RESET       | 35       | I-TTL | <b>Reset:</b> When this active low input is asserted the word alignment is reset. Upon release (low to high) the normal word alignment process is reinstated. Pin used for test purposes and is normally tied to V <sub>CC</sub> _TTL.                                  |

| WSYNCDSB     | 36       | I-TTL | <b>Word Sync Disable:</b> When high, disables resynchronization to word edge upon errors encountered in the C-field of the incoming encoded word. Pin used for test purposes and is normally tied low.                                                                  |

| NC           | 21<br>27 |       | No Connect: These pins should be left unconnected.                                                                                                                                                                                                                      |

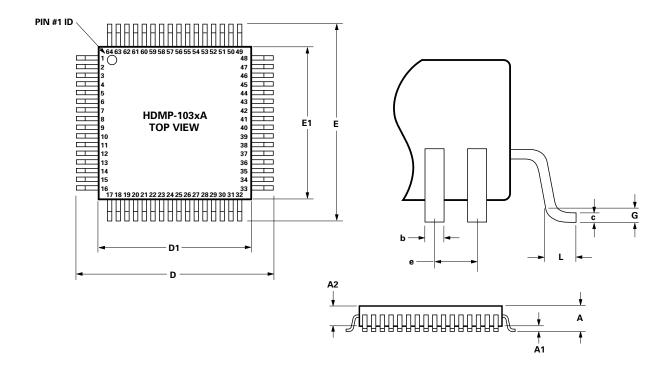

# **Package Information**

| ltem                                       | Details           |

|--------------------------------------------|-------------------|

| Package Material                           | Plastic           |

| Lead Finish Material                       | 85% Tin, 15% Lead |

| Lead Finish Thickness                      | 300–800 µm        |

| Lead Skew                                  | 0.20 mm max       |

| Lead Coplanarity<br>(seating plane method) | 0.10 mm max       |

# **Mechanical Dimensions**

| Mechanical Dimensions of HDMP-1032A/34A  |       |       |       |       |                 |      |               |                 |             |      |  |  |

|------------------------------------------|-------|-------|-------|-------|-----------------|------|---------------|-----------------|-------------|------|--|--|

| Dimensional Parameter<br>(in millmeters) | D1/E1 | D/E   | b     | e     | L               | C    | G             | A2              | A1          | Α    |  |  |

| HDMP-103xA                               | 14.00 | 17.20 | 0.35  | 0.80  | 0.88            | 0.17 | 0.25          | 2.00            | 0.25<br>Max | 2.35 |  |  |

| Tolerance                                | ±0.10 | ±0.25 | ±0.05 | Basic | +0.15/<br>-0.10 | Max  | Gage<br>Plane | +0.10/<br>-0.05 |             | Max  |  |  |

# **Appendix: Internal Architecture Information**

# **Line Code Description**

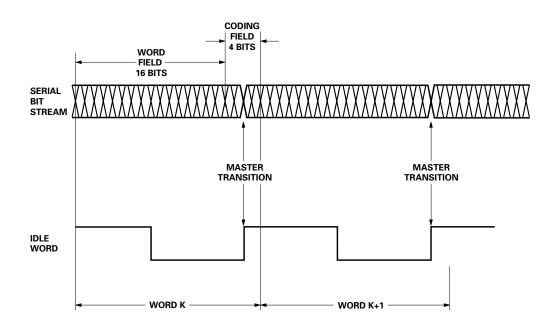

The HDMP-1032A/1034A line code is Conditional Invert Master Transition (CIMT) as illustrated in Figure 9. The CIMT line code uses three types of words: Data words, Control words, and Idle words. Idle words are generated internally by the Tx when both TXDATA and TXCNTL are low. Each word consists of a Word Field (W-Field) followed by a Coding Field (C-Field). The C-Field has a master transition. Users can send arbitrary information carried by Data or Control Words. The DC balance of the line code is enforced automatically by the Tx. Idle words have a single rising edge at the master transition when operating in non-enhanced simplex mode.

The coding definitions are summarized in the table on the next page. Note that the leftmost bit in each table is the first bit to be transmitted in time, while the rightmost bit is the last bit to be transmitted.

# **Data Word Codes**

In Data Word mode, all 16 bits of the Tx are transmitted to the Rx, along with a flag bit. If TXFLGENB=1, then the user controls this bit with TXFLAG; otherwise it is internally set to alternate.

# **Control Word Codes**

In Control Word mode, 14 bits are transmitted to the Rx. The lower 7 bits X0-X6 are sent in the w0-w6 space, and the upper 7 bits X7-X13 are sent in the w9-w15 space. Bits w7 and w8 are forced 01 for true, and 10 for inverted control words. The shifting of the word field is for backward compatibility with previous versions of G-Links chip sets.

#### **Idle Word and Error Codes**

Two Idle Words, IW1a and IW1b are provided. Unused word codes are mapped into Error States.

#### **Enhanced Simplex Mode**

In this mode (ESMPXENB=1), the flag bit is scrambled at the Tx and descrambled at the Rx. Since the Rx uses the scrambled flag bit for frame alignment, it is also defined for Control and Idle Words. However, the flag bit is only available to the user in the Data Word mode. The first bit w0 is also scrambled to aid word alignment.

Figure 9. HDMP-1032A/1034A (Tx/Rx Pair) Line Code.

# **Coding<sup>1</sup> with ESMPXENB=0** (Compatible with previous G-Link chips, HDMP-1012/14, HDMP-1022/24)

| Word Type               | Flag | W-   | Field | b  |    |    |    |     |    |    |      |     |     |     |     |     |      | C-I | Fiel | d  |    |

|-------------------------|------|------|-------|----|----|----|----|-----|----|----|------|-----|-----|-----|-----|-----|------|-----|------|----|----|

|                         |      | w0   | w1    | w2 | w3 | w4 | w5 | w6  | w7 | w8 | w9   | w10 | w11 | w12 | w13 | w14 | w15  | c0  | c1   | c2 | c3 |

| Data Word Structure     |      |      |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |     |      |    |    |

| Data = True             | 0    | X0   | X1    | X2 | Х3 | X4 | Х5 | X6  | Х7 | X8 | X9   | X10 | X11 | X12 | X13 | X14 | X15  | 1   | 1    | 0  | 1  |

| Data = Inverted         | 0    | #(X0 | X1    | X2 | Х3 | X4 | Х5 | X6  | Х7 | X8 | X9   | X10 | x11 | X12 | X13 | X14 | X15) | 0   | 0    | 1  | 0  |

| Data = True             | 1    | X0   | X1    | X2 | Х3 | X4 | Х5 | X6  | Х7 | X8 | X9   | X10 | X11 | X12 | X13 | X14 | X15  | 1   | 0    | 1  | 1  |

| Data = Inverted         | 1    | #(X0 | X1    | Х2 | Х3 | X4 | X5 | X6  | X7 | X8 | X9   | X10 | x11 | X12 | X13 | X14 | X15) | 0   | 1    | 0  | 0  |

| Control Word Structure  |      |      |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |     |      |    |    |

| Control = True          |      | X0   | X1    | X2 | Х3 | X4 | X5 | X6  | 0  | 1  | X7   | X8  | X9  | X10 | X11 | X12 | X13  | 0   | 0    | 1  | 1  |

| Control = Inverted      |      | #(X0 | X1    | Х2 | Х3 | Х4 | Х5 | X6) | 1  | 0  | #(X7 | X8  | X9  | X10 | X11 | X12 | X13) | 1   | 1    | 0  | 0  |

| Idle Word Structure     |      |      |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |     |      |    |    |

| Idle Word 1a            |      | 1    | 1     | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 0    | 0   | 0   | 0   | 0   | 0   | 0    | 0   | 0    | 1  | 1  |

| Idle Word 1b            |      | 1    | 1     | 1  | 1  | 1  | 1  | 1   | 0  | 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0    | 0   | 0    | 1  | 1  |

| Detectable Error States |      |      |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |     |      |    |    |

|                         |      | d    | d     | d  | d  | d  | d  | d   | d  | d  | d    | d   | d   | d   | d   | d   | d    | d   | 0    | 0  | d  |

|                         |      | d    | d     | d  | d  | d  | d  | d   | d  | d  | d    | d   | d   | d   | d   | d   | d    | d   | 1    | 1  | d  |

|                         |      | d    | d     | d  | d  | d  | d  | d   | 0  | d  | d    | d   | d   | d   | d   | d   | d    | 1   | 1    | 0  | 0  |

|                         |      | d    | d     | d  | d  | d  | d  | d   | 1  | 1  | d    | d   | d   | d   | d   | d   | d    | 1   | 1    | 0  | 0  |

|                         |      | d    | d     | d  | d  | d  | d  | d   | d  | d  | d    | d   | d   | d   | d   | d   | d    | 1   | 0    | 1  | 0  |

|                         |      | d    | d     | d  | d  | d  | d  | d   | d  | d  | d    | d   | d   | d   | d   | d   | d    | 0   | 1    | 0  | 1  |

# Coding<sup>1</sup> with ESMPXENB=1

| Word Type                      | Flag <sup>2</sup> | <b>W</b> -      | Field | 1  |    |    |    |     |    |    |      |     |     |     |     |     |      | C- | Fiel | d  |    |

|--------------------------------|-------------------|-----------------|-------|----|----|----|----|-----|----|----|------|-----|-----|-----|-----|-----|------|----|------|----|----|

|                                |                   | w0 <sup>3</sup> | w1    | w2 | w3 | w4 | w5 | w6  | w7 | w8 | w9   | w10 | w11 | w12 | w13 | w14 | w15  | c0 | c1   | c2 | c3 |

| Data Word Structure            |                   |                 |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |    |      |    |    |

| Data = True                    | 0                 | X0              | X1    | X2 | Х3 | X4 | X5 | X6  | Х7 | X8 | X9   | X10 | X11 | X12 | X13 | X14 | X15  | 1  | 1    | 0  | 1  |

| Data = Inverted                | 0                 | #(X0            | X1    | X2 | Х3 | Х4 | X5 | X6  | Х7 | X8 | X9   | X10 | x11 | X12 | X13 | X14 | X15) | 0  | 0    | 1  | 0  |

| Data = True                    | 1                 | X0              | X1    | X2 | Х3 | X4 | X5 | X6  | Х7 | X8 | X9   | X10 | X11 | X12 | X13 | X14 | X15  | 1  | 0    | 1  | 1  |

| Data = Inverted                | 1                 | #(X0            | X1    | X2 | Х3 | X4 | X5 | X6  | Х7 | X8 | X9   | X10 | x11 | X12 | X13 | X14 | X15) | 0  | 1    | 0  | 0  |

| <b>Control Word Structure</b>  |                   |                 |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |    |      |    |    |

| Control = True                 | 0                 | X0              | X1    | X2 | Х3 | Х4 | X5 | X6  | 0  | 1  | X7   | X8  | X9  | X10 | X11 | X12 | X13  | 0  | 0    | 1  | 1  |

| Control = Inverted             | 0                 | #(X0            | X1    | X2 | Х3 | X4 | X5 | X6) | 1  | 0  | #(X7 | X8  | X9  | X10 | X11 | X12 | X13) | 1  | 1    | 0  | 0  |

| Control = True                 | 1                 | X0              | X1    | X2 | Х3 | Х4 | X5 | X6  | 0  | 1  | X7   | X8  | X9  | X10 | X11 | X12 | X13  | 0  | 1    | 0  | 1  |

| Control = Inverted             | 1                 | #(X0            | X1    | X2 | Х3 | X4 | X5 | X6) | 1  | 0  | #(X7 | X8  | X9  | X10 | X11 | X12 | X13) | 1  | 0    | 1  | 0  |

| Idle Word Structure            |                   |                 |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |    |      |    |    |

| Idle Word 1a                   | 0                 | 1               | 1     | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 0    | 0   | 0   | 0   | 0   | 0   | 0    | 0  | 0    | 1  | 1  |

| Idle Word 1b                   | 0                 | 1               | 1     | 1  | 1  | 1  | 1  | 1   | 0  | 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0    | 0  | 0    | 1  | 1  |

| Idle Word 1a                   | 1                 | 1               | 1     | 1  | 1  | 1  | 1  | 1   | 1  | 1  | 0    | 0   | 0   | 0   | 0   | 0   | 0    | 0  | 1    | 0  | 1  |

| Idle Word 1b                   | 1                 | 1               | 1     | 1  | 1  | 1  | 1  | 1   | 0  | 0  | 0    | 0   | 0   | 0   | 0   | 0   | 0    | 0  | 1    | 0  | 1  |

| <b>Detectable Error States</b> |                   |                 |       |    |    |    |    |     |    |    |      |     |     |     |     |     |      |    |      |    |    |